5.4.3. 存储电路

存储电路用于构建用于存储二进制值的计算机内存。由存储电路构建的计算机内存类型称为静态 RAM (SRAM)。它用于构建 CPU 寄存器存储和片上高速缓存。系统通常使用动态 RAM (DRAM) 作为主存储器 (RAM) 存储。DRAM 的基于电容器的设计要求定期用其存储的值进行刷新,因此有“动态”的绰号。SRAM 是基于电路的存储,不需要刷新其值,因此被称为静态 RAM。基于电路的内存比基于电容器的内存更快,但更昂贵。因此,SRAM 往往用于内存层次结构 (CPU 寄存器和片上高速缓存)顶部的存储,而 DRAM 用于主存储器 (RAM) 存储。在本章中,我们重点介绍基于电路的存储器,例如 SRAM。

要存储一个值,电路必须包含一个反馈回路,以便电路保留该值。换句话说,存储电路的值取决于其输入值以及其当前存储的值。当电路存储一个值时,其当前存储的值和其输入一起产生与当前存储的值匹配的输出(即电路继续存储相同的值)。当将新值写入存储电路时,电路的输入值会瞬间改变以修改电路的行为,从而导致新值被写入并存储在电路中。写入后,电路将恢复存储新写入值的稳定状态,直到下一次写入电路。

RS锁存器

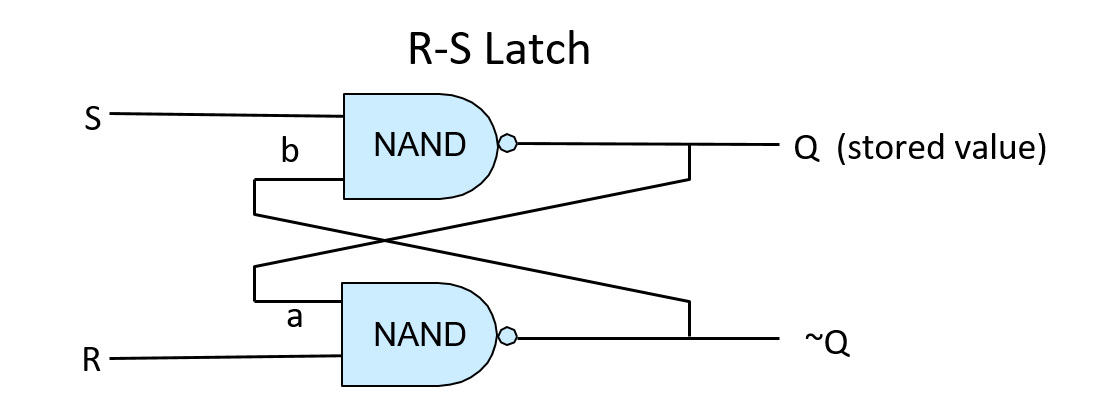

锁存器是一种存储(或记住)1 位值的数字电路。一个例子是 复位锁存器 (或 RS 锁存器)。RS 锁存器有两个输入值 S 和 R,以及一个输出值 Q,该输出值也是存储在锁存器中的值。RS 锁存器还可以输出 NOT(Q),即存储值的负数。图 1 显示了用于存储单个位的 RS 锁存器电路。

图 1. RS 锁存电路存储 1 位值。

关于 RS 锁存器,首先要注意的是从其输出到其输入的反馈回路:顶部 NAND 门 (Q) 的输出是 (a) 底部 NAND 门的输入,底部 NAND 门的输出 (~Q) 是 (b) 顶部 NAND 门的输入。当输入 S 和 R 都为 1 时,RS 锁存器存储值 Q。换句话说,当 S 和 R 都为 1 时,RS 锁存器输出值 Q 是稳定的。要查看此行为,请考虑图 2;这显示了一个存储值 1(Q 为 1)的 RS 锁存器。当 R 和 S 都为 1 时,底部 NAND 门的反馈输入值 (a) 是 Q 的值,即 1,因此底部 NAND 门的输出为 0(1 NAND 1 为 0)。顶部 NAND 门的反馈输入值 (b) 是底部 NAND 门的输出,为 0。顶部 NAND 门的另一个输入是 1,即 S 的值。顶部门的输出为 1(1 NAND 0 为 1)。因此,当 S 和 R 均为 1 时,该电路会持续存储 Q 的值(本例中为 1)。

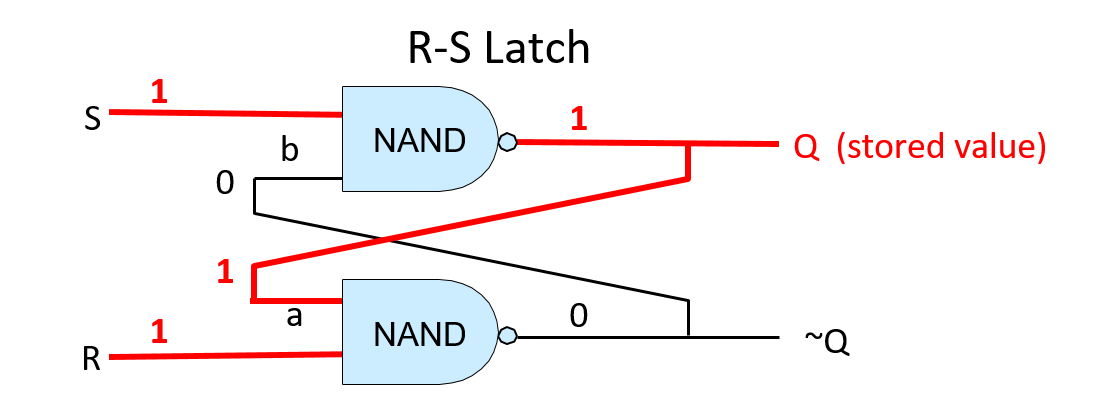

图 2. 存储 1 位值的 RS 锁存器。当锁存器存储值时,R 和 S 均为 1。存储的值是输出 Q。

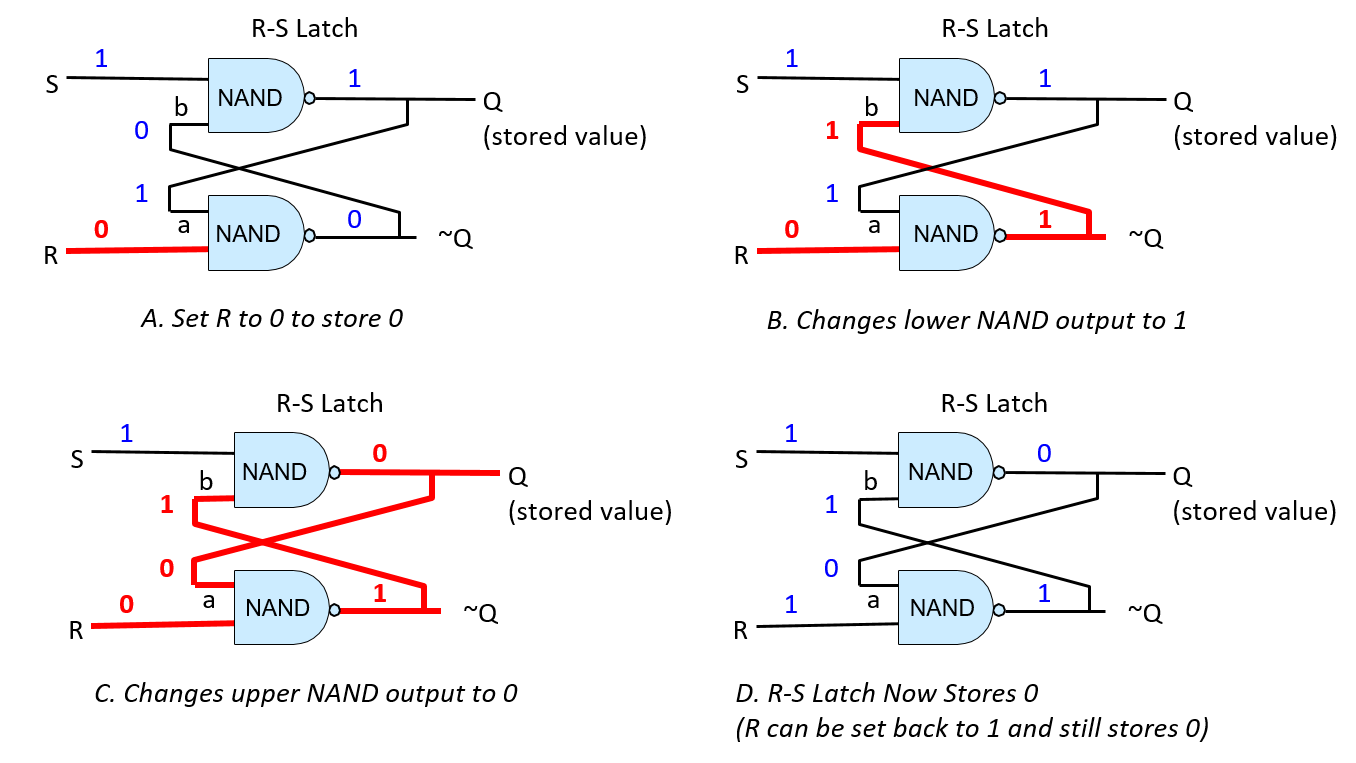

要更改 RS 锁存器中存储的值,必须将 R 或 S 中的一个的值设置为 0。当锁存器存储新值时,R 和 S 将重新设置为 1。RS 锁存器周围的控制电路确保 R 和 S 永远不会同时为 0:它们中最多只有一个值为 0,并且 R 或 S 中的一个值为 0 表示正在将值写入 RS 锁存器。要将值 0 存储在 RS 锁存器中,必须将输入 R 设置为 0(S 的值保持为 1)。要将值 1 存储在 RS 锁存器中,必须将输入 S 设置为 0(R 的值保持为 1)。例如,假设 RS 锁存器当前存储的是 1。要将 0 写入锁存器,R 的值需设置为 0。这意味着值 0 和 1 被输入到下方的 NAND 门,其计算结果为 (0 NAND 1),即 1。该输出值 1 也是上方 NAND 门的输入 b(如 图 3 B 所示)。有了新的 b 输入值 1 和 S 输入值 1,上方 NAND 门为 Q 计算出一个新的输出值 0,该输出值也作为输入 a 馈入下方的 NAND 门(如 图 3 C 所示)。当 a 的值为 0 且 b 的值为 1 时,锁存器现在存储 0。当 R 最终设置回 1 时,RS 锁存器继续存储值 0(如 图 3 D 所示)。

图 3. 要将 0 写入 RS 锁存器,请暂时将 R 设置为 0。

门控 D 锁存器

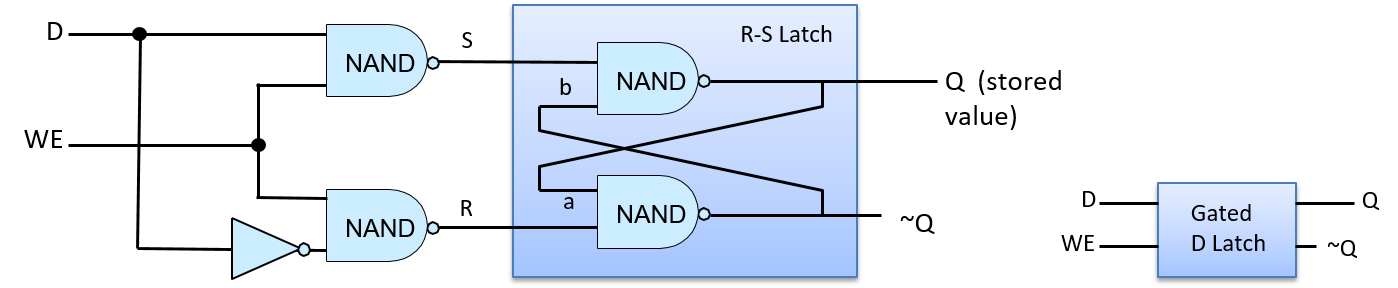

门控 D 锁存器 在 RS 锁存器中添加电路,以确保它永远不会同时接收 R 和 S 的 0 输入。图 4 显示了门控 D 锁存器的构造。

图 4. 门控 D 锁存器存储 1 位值。其第一组 NAND 门控制对 RS 锁存器的写入,并确保 R 和 S 的值永远不会同时为 0。

门控 D 锁存器的数据输入 (D) 是要存储到电路中的值(0 或 1)。写入控制 (WE) 输入控制将值写入 RS 锁存器。当 WE 为 0 时,两个 NAND 门的输出均为 1,导致 RS 锁存器的 S 和 R 输入值为 1(RS 锁存器存储一个值)。仅当 WE 为 1 时,门控 D 锁存器才会将 D 的值写入 RS 锁存器。由于数据输入 (D) 值在发送到底部 NAND 门之前被反转,因此顶部或底部 NAND 门输入中只有一个的输入为 1。这意味着当 WE 位为 1 时,R 或 S 中恰好有一个为 0。例如,当 D 为 1 且 WE 为 1 时,顶部 NAND 计算(1 NAND 1),底部 NAND 门计算(O NAND 1)。因此,顶部 NAND 门对 S 的输入为 0,底部 NAND 门对 R 的输入为 1,从而将值 1 写入 RS 锁存器。当 WE 输入为 0 时,两个 NAND 门均输出 1,使 R 和 S 保持为 1。换句话说,当 WE 为 0 时,D 的值对存储在 RS 锁存器中的值没有影响;只有当 WE 为 1 时,D 的值才会写入锁存器。要将另一个值写入门控 D 锁存器,请将 D 设置为要存储的值,并将 WE 设置为 1。

CPU 寄存器

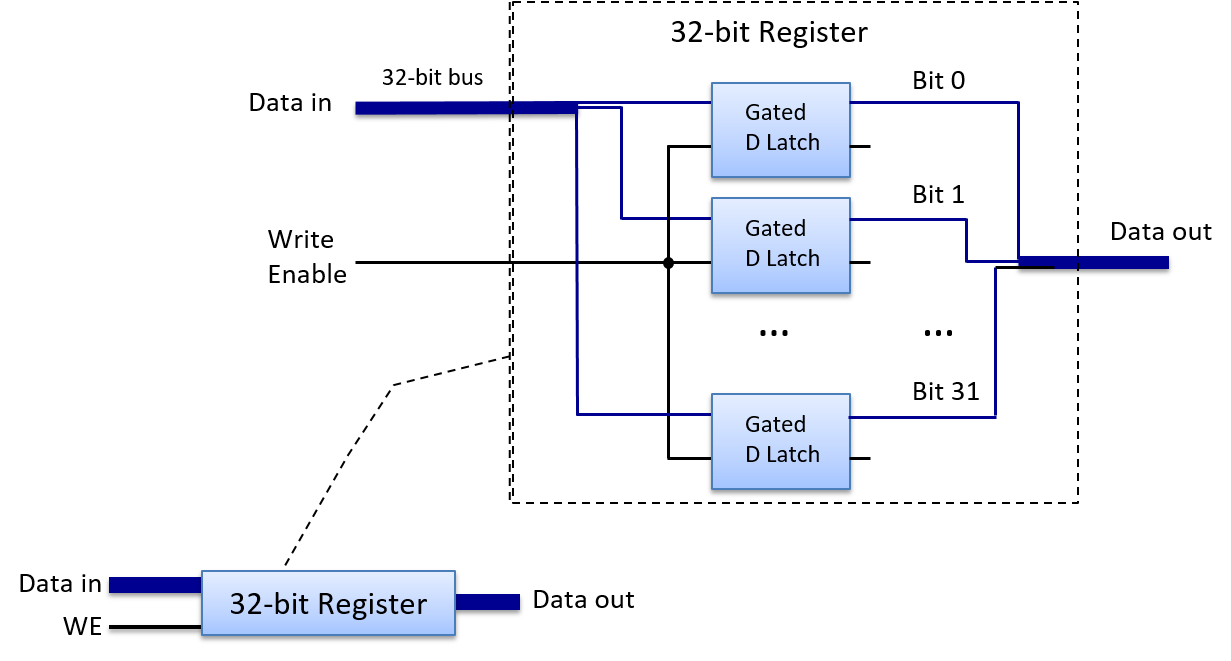

多位存储电路是通过将多个 1 位存储电路连接在一起而构建的。例如,将 32 个 1 位 D 锁存器组合在一起可产生一个 32 位存储电路,该存储电路可用作 32 位 CPU 寄存器,如 图 5 所示。寄存器电路有两个输入值:一个 32 位数据值和一个 1 位写使能信号。在内部,每个 1 位 D 锁存器将寄存器的 32 位 Data in 输入中的一位作为其 D 输入,并且每个 1 位 D 锁存器将寄存器的 WE 输入作为其 WE 输入。寄存器的输出是存储在组成寄存器电路的 32 个 1 位 D 锁存器中的 32 位值。

图 5. CPU 寄存器由多个门控 D 锁存器组成(32 位寄存器有 32 个)。当其 WE 输入为 1 时,数据输入将写入寄存器。其数据输出是存储的值。